九州大学 システム情報科学府 情報理工学専攻 2023年度 計算機アーキテクチャ

Author

Yu

Description

【問 1】

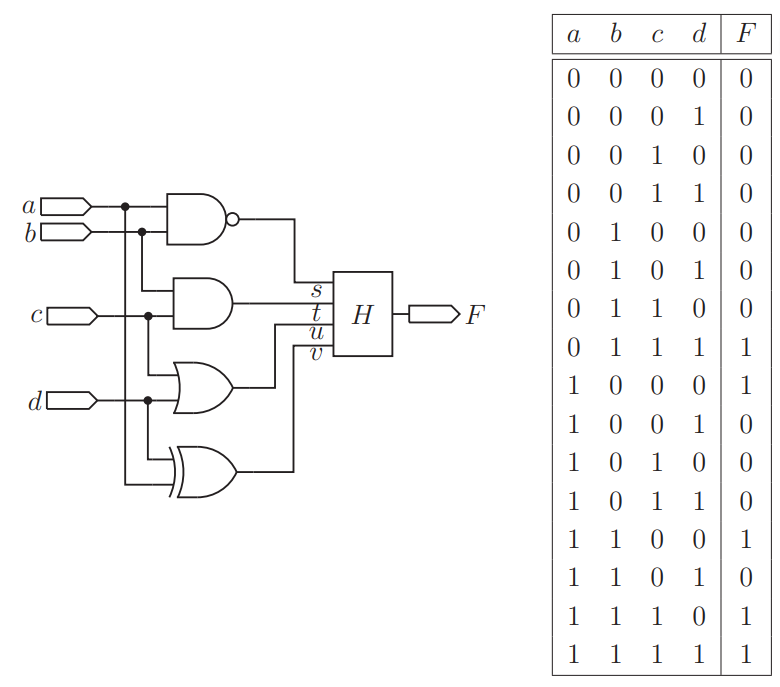

下図の様にいくつかの論理ゲートと部分回路 \(H\) から構成される論理回路の出力の論理関数 \(F(a, b, c, d)\) が以下の様な真理値表で表される時, 部分回路 \(H\) の論理関数 \(H(s,t, u, v)\)の最簡積和形を示せ. ただし,論理関数の最簡積和形とはその論理関数を表す積和形論理式のうち,積項数が最小のものを指す. 積項数が等しい積和形論理式が複数ある場合にはそのなかでリテラル数が最小のものを指す.

【問 2】

パイプライン式データパスを有するマイクロプロセッサについて考える. 以下の式で示すように,プログラム実行時間 \(ET\) は,プログラム実行のために処理される総命令数 \(IC\), クロックサイクル当り実行命令数 \(IPC\),ならびに,動作周波数 \(F\),の \(3\) つのパラメータを用いて表現できる.

以下の各問いに答えよ.

(1) 命令発行幅が \(1\) のインオーダマイクロプロセッサを考える. シングルサイクル・データパス方式( \(1\) 命令の実行を \(1\) クロックサイクルで処理する方式)と比較した場合, パイプライン式データパスの実装が \(IC,IPC,F\) に与える影響をそれぞれ説明せよ. なお,各パラメータにおいて影響がない場合は「影響なし」と答えること.

(2) このパイプライン式データパスにおいて命令発行幅を \(2\) へ増加し, インオーダ命令実行のスーパスカラ方式へと拡張した(依存関係のない命令を最大で \(2\) 個同時に実行できる). この拡張が \(IC,IPC,F\) に与える影響をそれぞれ説明せよ. なお,各パラメータにおいて影響がない場合は「影響なし」と答えること.

(3) 命令発行幅は \(4\) と仮定する.このパイプラインで達成できる \(IPC\) の上限を答えよ.

【問 3】

コンピュータのメモリシステムについて考える. マイクロプロセッサにダイレクトマップ・キャッシュが搭載されているものとする. ワードアドレッシング方式を採用しており,ワードサイズは \(4\) バイト,キャッシュ・サイズは \(16\) バイト,ブロックサイズは \(4\) バイト,アドレス長は \(4\) ビットである. キャッシュの初期状態は空であったが,これまでに \(1101 \Rightarrow 1010 \Rightarrow 1111 \Rightarrow 1101\) のワードアドレス (2 進表現) に対してメモリアクセスが順次発生している. このとき,メモリアクセス (i) ~ (v) が順次発生したとする.

| メモリアクセス | ワードアドレス (2 進表現) |

|---|---|

| (i) | 1010 |

| (ii) | 1001 |

| (iii) | 1000 |

| (iv) | 0011 |

| (v) | 1111 |

以下の各問いに答えよ.

(1) メモリアクセス (i) ~ (v) のうち,キャッシュ・ヒットとなるメモリアクセスをすべて答えよ. 該当するメモリアクセスがない場合は「該当なし」と答えること.

(2) メモリアクセス (i) ~ (v) のうち,初期参照ミスとなるメモリアクセスをすべて答えよ. 該当するメモリアクセスがない場合は「該当なし」と答えること.

(3) 競合ミスを削減するためにはこのキャッシュをどのように改良すれば良いか説明せよ. また,改良によるデメリットがあればあわせて説明せよ.

Kai

【問 1】

| a | b | c | d | s | t | u | v | F |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| s | t | u | v | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | x |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | x |

| 0 | 1 | 0 | 0 | x |

| 0 | 1 | 0 | 1 | x |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | x |

| 1 | 1 | 0 | 1 | x |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

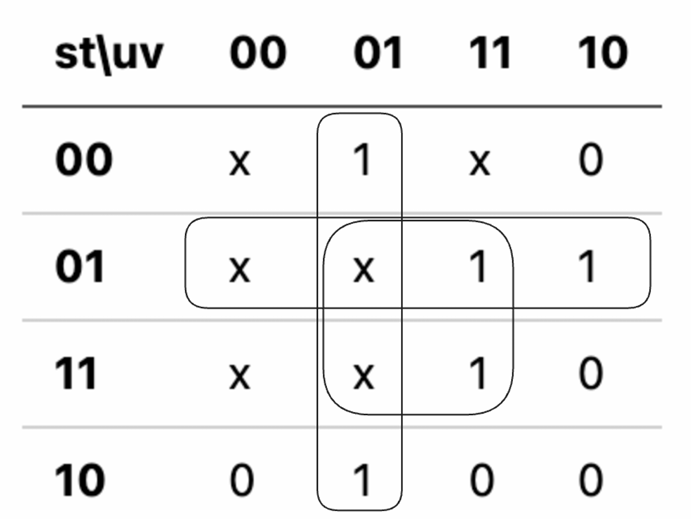

| st\uv | 00 | 01 | 11 | 10 |

|---|---|---|---|---|

| 00 | x | 1 | x | 0 |

| 01 | x | x | 1 | 1 |

| 11 | x | x | 1 | 0 |

| 10 | 0 | 1 | 0 | 0 |

【問 2】

(1)

- IC: 影響なし

- IPC: 低下する可能性がある

- F: より⾼い

(2)

- IC: 影響なし

- IPC: より⾼い

- F: より低い

(3)

【問 3】

(1)

(i)

(2)

(iii)

(3)

- キャッシュサイズの拡張

- セットアソシアティブキャッシュの採⽤

デメリット: ハードウェアコストが上がり