東京大学 情報理工学系研究科 電子情報学専攻 2017年8月実施 専門 第2問

Author

Description

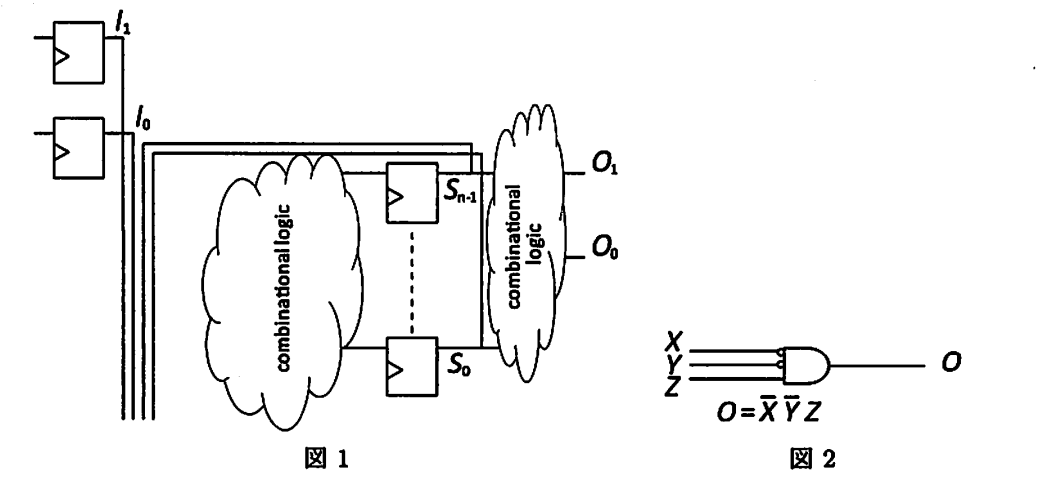

以下のような剰余計算回路

(1)

(2) (1) で設計した状態遷移図の状態遷移表を下表のように示せ。ここで状態は

(3) 状態レジスタの各ビットの次状態を決定する論理式を、それぞれ加法標準形(積項を+でつないで出来た式)で示せ。カルノー図を用いて項数を最小とすること。

(4) 図

Kai

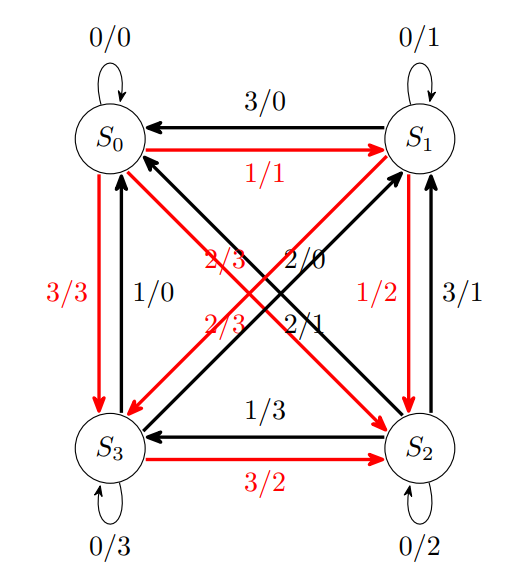

(1)

求める最も状態数の少ない状態遷移図は次の通り。

(2)

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 |

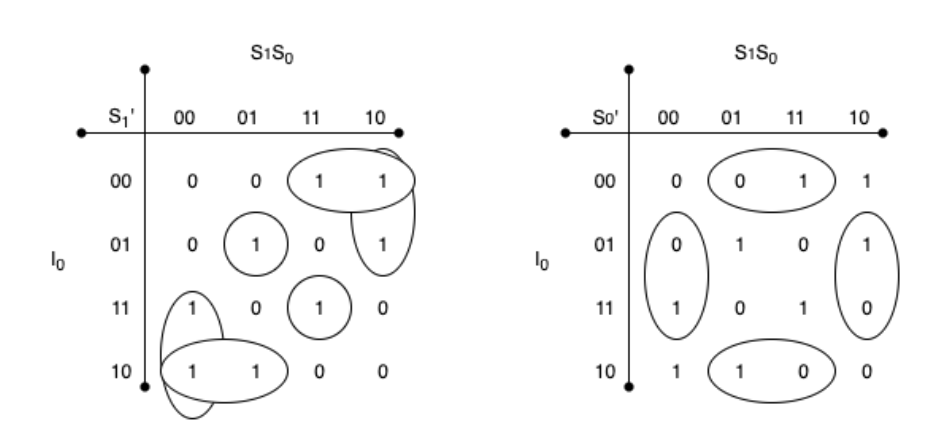

(3)

カルノー図は次の通り。

よって加法標準形は

(4)

TODO