東京大学 情報理工学系研究科 電子情報学専攻 2016年8月実施 専門 第2問

Author

Description

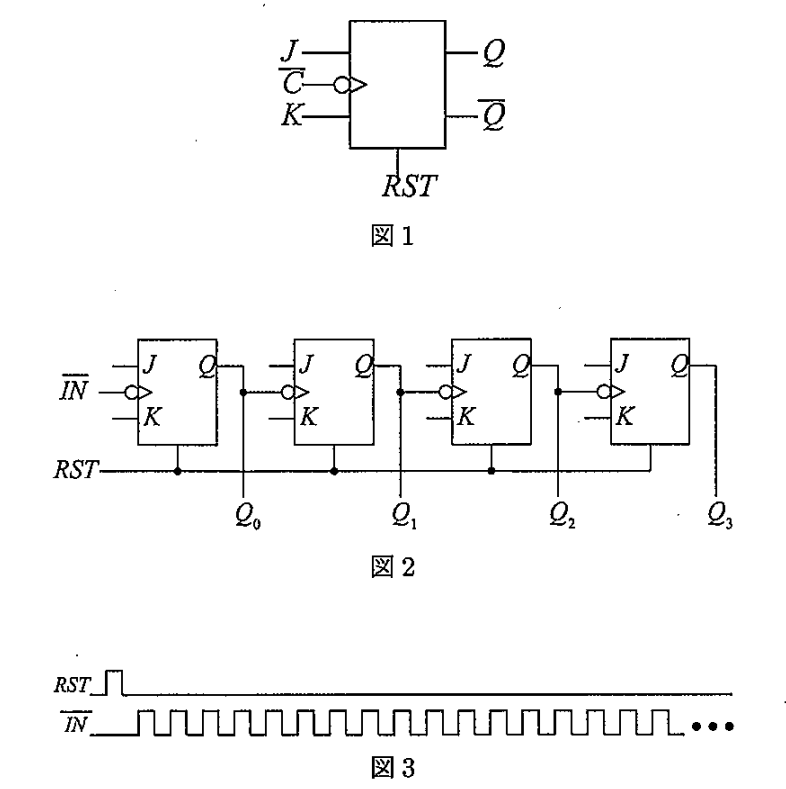

Let us consider a falling-edge-triggered JK flip-flop as shown in Fig.1. This JK flip-flop is reset to

(1) Let us assume a 4-bit counter as shown in Fig.2, and the input signals shown in Fig.3 are given to the counter. Show a time chart of the outputs

(2) Modify the circuit in Fig.2 so that the outputs

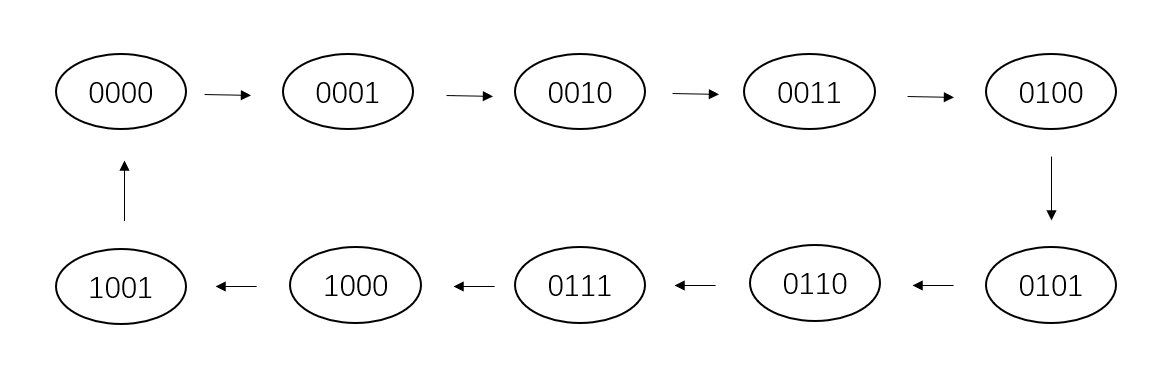

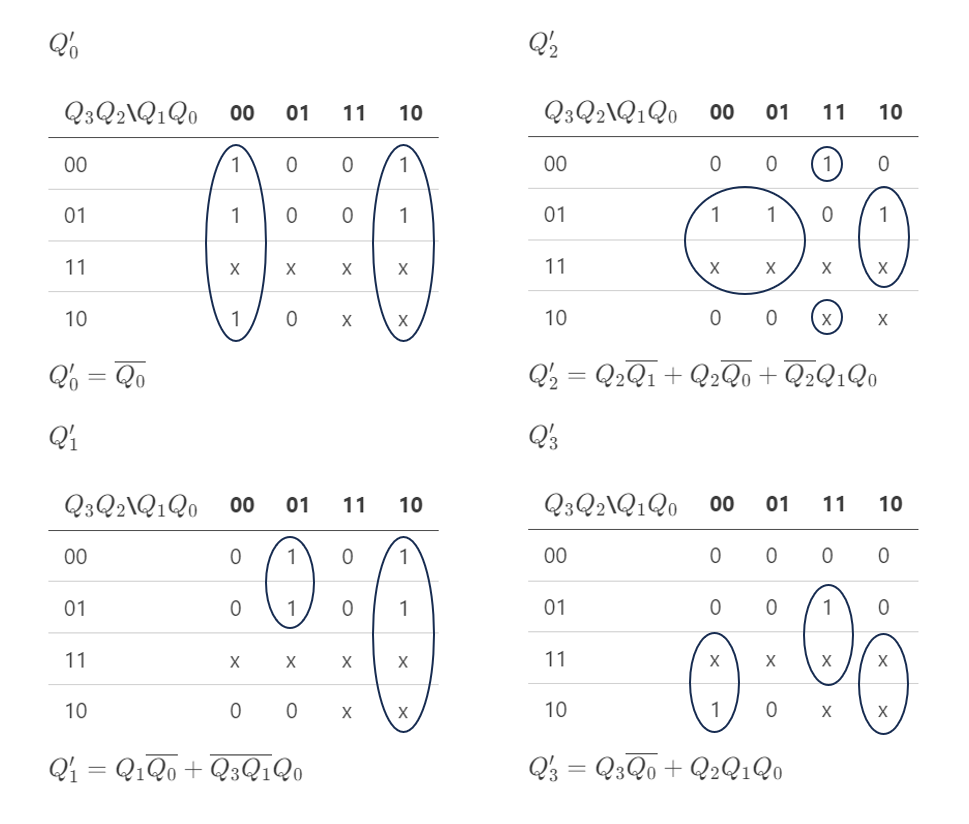

(3) Let us design a parallel decimal counter. A decimal counter is a circuit that starts counting from (

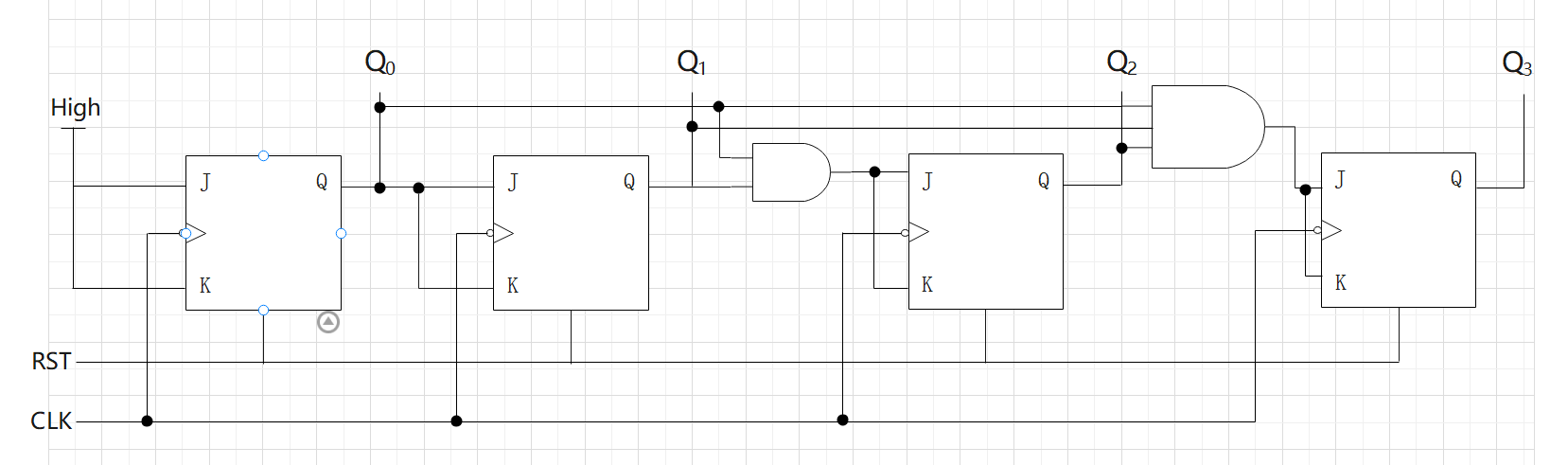

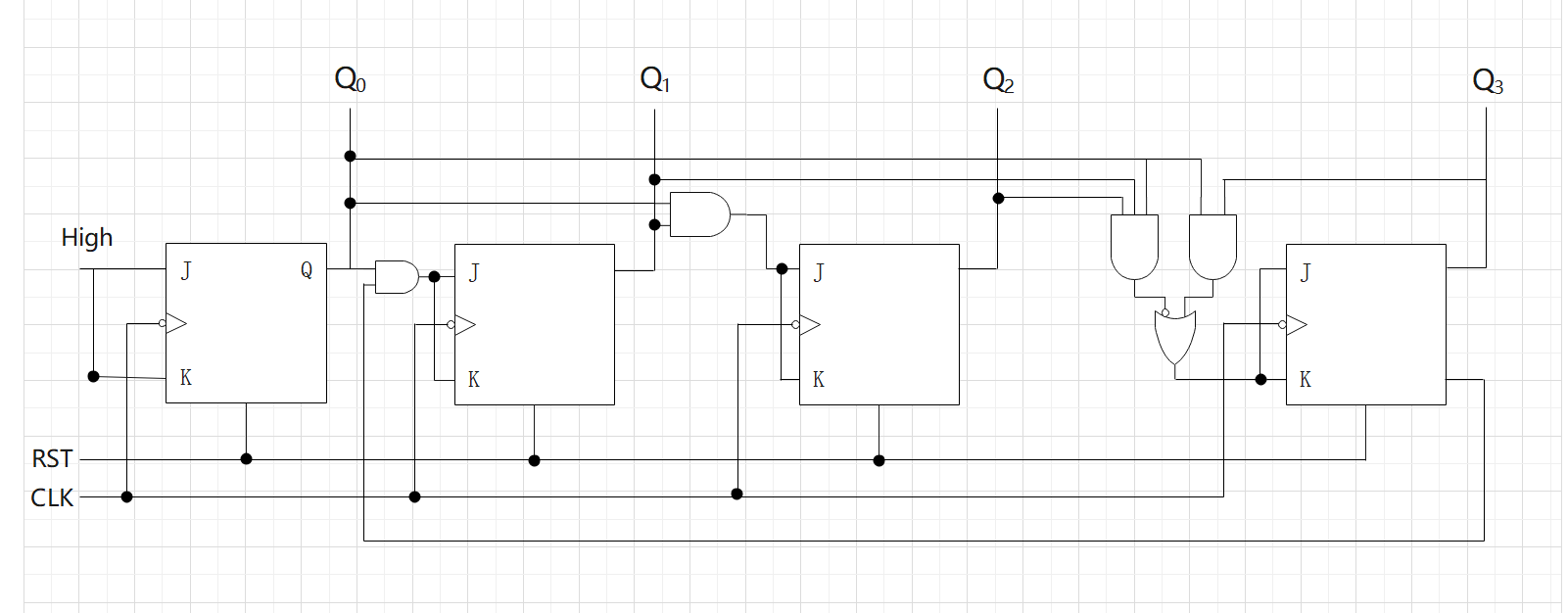

(4) Show a schematic of a parallel decimal counter by using the results in (3).

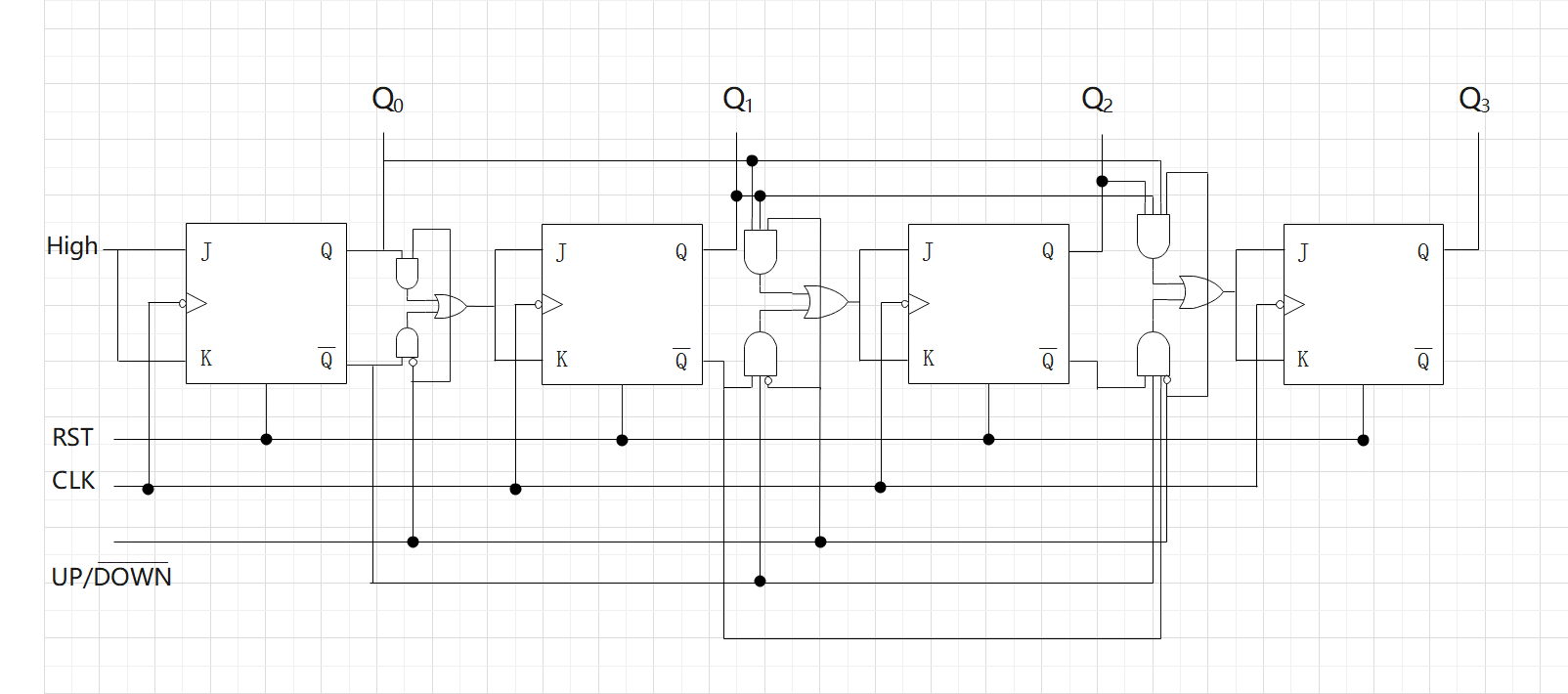

(5) Modify the circuit in (2) to an up/down counter and show its schematic. An up/down counter is a counter whose operation mode can be changed either to count-up or count-down by a control signal

Kai

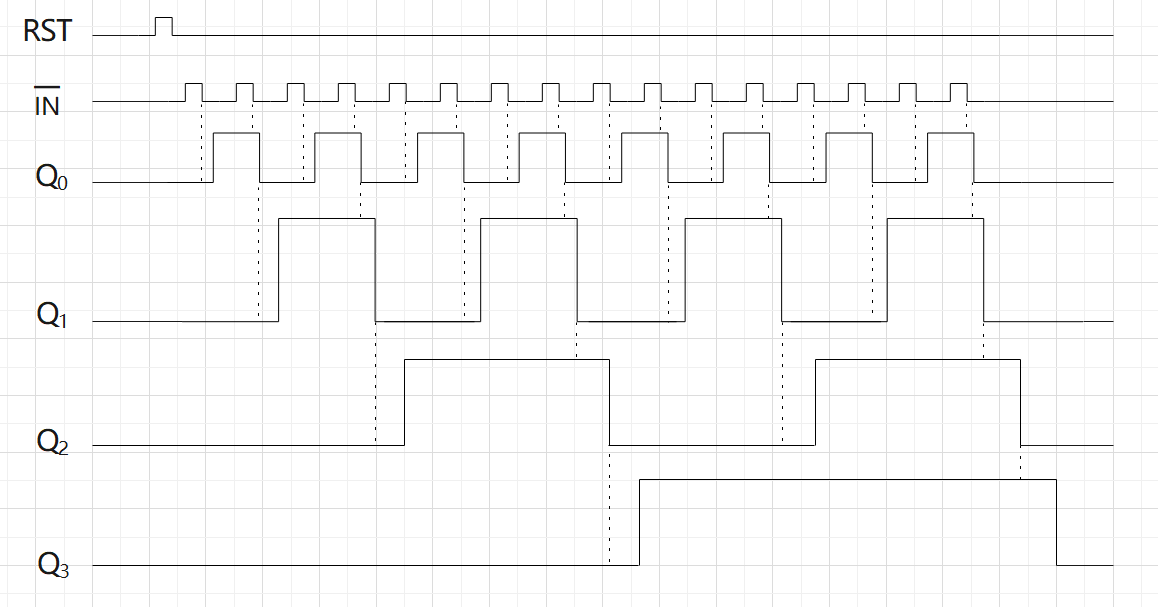

(1)

(2)

(3)

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

(4)

(5)