東京大学 情報理工学系研究科 創造情報学専攻 2008年8月実施 筆記試験 第2問

Author

Description (English)

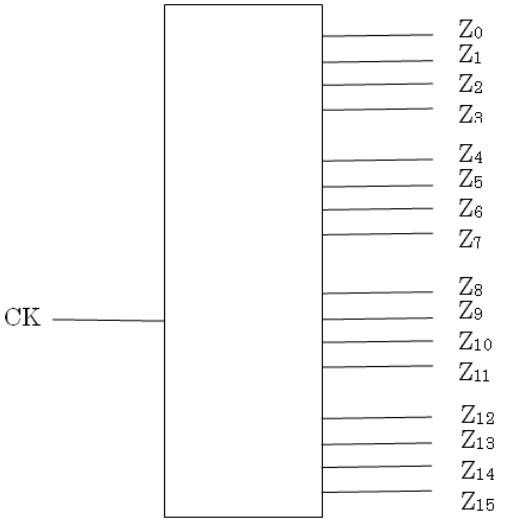

Consider an

a. A one digit decimal is represented by 4 bits.

b. The counter is synchronous and has a clock CK,

c. The initial value of the counter is 0, namely,

d. The value of the counter increases by 1 at every input of the clock. When the value of the counter reaches the maximum value, the next clock input sets the output to be 0.

For example, the following figure depicts the input (the clock CK) and the output (

(1) Draw a table or a diagram showing the state-transition for the case

(2) Construct the logic circuit of the counter for the case

(3) Construct the logic circuit of the counter for the case

(4) For a given