九州大学 システム情報科学府 情報理工学専攻 2022年8月実施 計算機アーキテクチャ

Author

Description

【問 1】

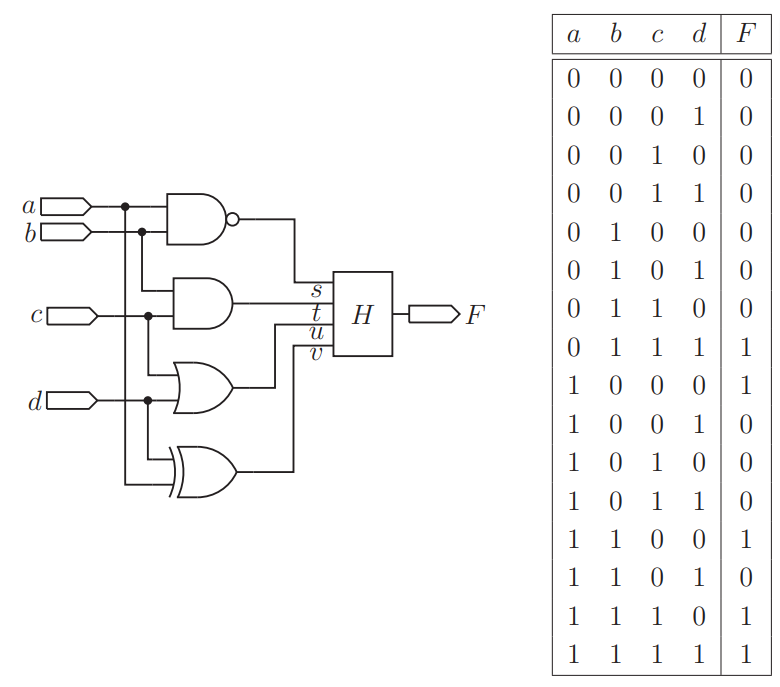

下図の様にいくつかの論理ゲートと部分回路

【問 2】

パイプライン式データパスを有するマイクロプロセッサについて考える.

以下の式で示すように,プログラム実行時間

以下の各問いに答えよ.

(1) 命令発行幅が

(2) このパイプライン式データパスにおいて命令発行幅を

(3) 命令発行幅は

【問 3】

コンピュータのメモリシステムについて考える.

マイクロプロセッサにダイレクトマップ・キャッシュが搭載されているものとする.

ワードアドレッシング方式を採用しており,ワードサイズは

| メモリアクセス | ワードアドレス (2 進表現) |

|---|---|

| (i) | 1010 |

| (ii) | 1001 |

| (iii) | 1000 |

| (iv) | 0011 |

| (v) | 1111 |

以下の各問いに答えよ.

(1) メモリアクセス (i) ~ (v) のうち,キャッシュ・ヒットとなるメモリアクセスをすべて答えよ. 該当するメモリアクセスがない場合は「該当なし」と答えること.

(2) メモリアクセス (i) ~ (v) のうち,初期参照ミスとなるメモリアクセスをすべて答えよ. 該当するメモリアクセスがない場合は「該当なし」と答えること.

(3) 競合ミスを削減するためにはこのキャッシュをどのように改良すれば良いか説明せよ. また,改良によるデメリットがあればあわせて説明せよ.

Kai

【問 1】

| a | b | c | d | s | t | u | v | F |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

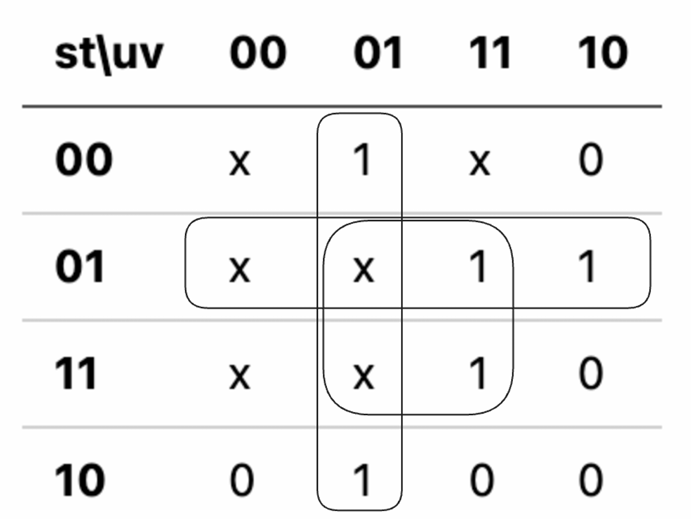

| s | t | u | v | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | x |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 1 | x |

| 0 | 1 | 0 | 0 | x |

| 0 | 1 | 0 | 1 | x |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | x |

| 1 | 1 | 0 | 1 | x |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

| st\uv | 00 | 01 | 11 | 10 |

|---|---|---|---|---|

| 00 | x | 1 | x | 0 |

| 01 | x | x | 1 | 1 |

| 11 | x | x | 1 | 0 |

| 10 | 0 | 1 | 0 | 0 |

【問 2】

(1)

- IC: 影響なし

- IPC: 低下する可能性がある

- F: より⾼い

(2)

- IC: 影響なし

- IPC: より⾼い

- F: より低い

(3)

【問 3】

(1)

(i)

(2)

(iii)

(3)

- キャッシュサイズの拡張

- セットアソシアティブキャッシュの採⽤

デメリット: ハードウェアコストが上がり