九州大学 システム情報科学府 情報理工学専攻 2021年8月実施 計算機アーキテクチャ

Author

Description

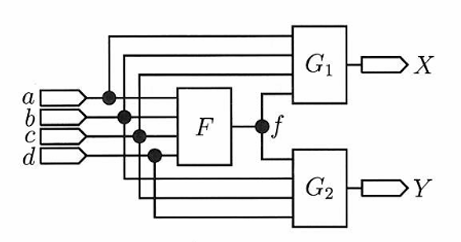

【問 1】

下図の論理回路の出力

【問 2】

5つのステージからなるパイプライン型データパスを有するインオーダ・マイクロプロセッサについて考える。

実装されたパイプラインステージは、IF(命令取得)、ID(命令デコード)、EX(実行)、MEM(メモリアクセス)、ならびに、WB(ライトバック)である。

加算命令の実行における各ステージの処理内容は以下の表に従う。

ここで、各パイプラインステージの実行は常に

パイプライン式データパスの動作

| ステージ | 加算命令(add |

|---|---|

| IF | メモリより実行すべき命令を取得し、次命令取得のためにプログラム・カウンタを更新 |

| ID | 命令の解読。レジスタファイルからレジスタ |

| EX | レジスタファイルから読み出した |

| MEM | 特に無し(加算結果をWBステージへ転送)。 |

| WB | 加算結果をレジスタファイル内のレジスタ $x に書き込み。 |

(1) 以下に示すアセンブリプログラムについて考える。各行において # 記号から右はコメントである。プログラム中に存在するフロー依存関係について、どの命令が、どの命令のどのレジスタに関して依存しているかをすべて列挙せよ。

add $1 ,$3, $5 # <1>

add $9 ,$2, $3 # <2>

add $6 ,$3, $3 # <3>

add $3 ,$4, $3 # <4>

add $4 ,$7, $1 # <5>

add $5 ,$7, $4 # <6>

add $9 ,$3, $6 # <7>

add $2 ,$7, $6 # <8>

(2) 命令発行幅は

(3) 命令パイプラインの命令発行幅を

(4) 上記 (3) の拡張によりクロック周波数が

【問 3】

キャッシュメモリにおける「初期参照ミス」「競合性ミス」「容量性ミス」とは何かそれぞれ説明せよ。

Kai

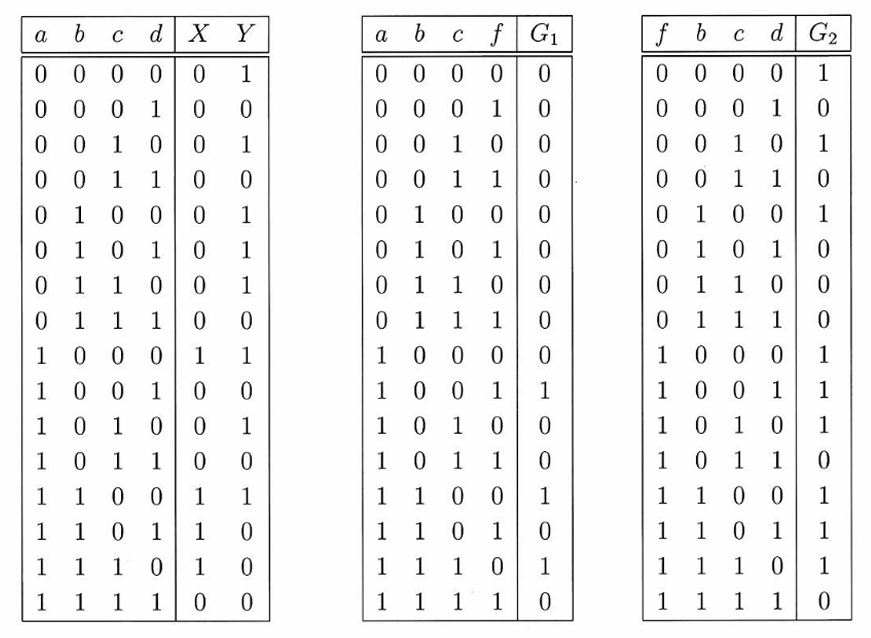

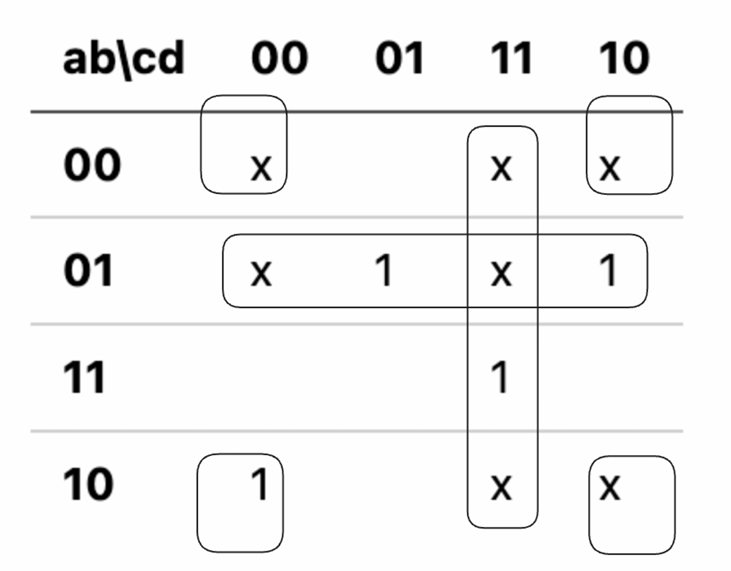

【問 1】

| a | b | c | d | f |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | x |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | x |

| 0 | 0 | 1 | 1 | x |

| 0 | 1 | 0 | 0 | x |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | x |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | x |

| 1 | 0 | 1 | 1 | x |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

【問 2】

(1)

(2)

14

(3)

12

(4)

1.11

【問 3】

初期参照ミス:キャッシュラインを最初にアクセスするときに起こるミス

競合性ミス:同じインデクスをもつ異なるキャッシュラインにアクセスすることで起こるミス

容量性ミス:キャッシュしたいライン数がキャッシュ容量を上回ることで起こるミス